- #Vivado tools for mac verification

- #Vivado tools for mac software

- #Vivado tools for mac simulator

- #Vivado tools for mac download

When using ModelSim, you must set the time resolution to ps or finer. It was only tested in ModelSim, but other simulators are expected to work as well. ISim will not unfortunately as it needs excessive amounts of system RAM when running the testbench. ModelSim also works fine when you have the Xilinx libraries correctly imported.

#Vivado tools for mac verification

If you have GHDL and make installed, you can start a basic functional verification in a behavioral simulation of the core by simply running. Using the core currently requires an installation of Xilinx ISE In preparation for both running the testbench and using the MAC in a project, please follow these steps. This page is a short overview of the features and usage of the MAC. The user interface is comprised of two FIFOs with a 8-bit data bus for packet transmission and reception, respectively. Only essential Ethernet functionality is supported. Its main distinction is the focus on simplicity both in the external user interface and internal operation.

#Vivado tools for mac download

If nothing happens, download the GitHub extension for Visual Studio and try again. If nothing happens, download Xcode and try again. If nothing happens, download GitHub Desktop and try again.

#Vivado tools for mac software

Looking for team-based training, or other locations?Ĭomplete an enquiry form and a Doulos representative will get back to you.GitHub is home to over 40 million developers working together to host and review code, manage projects, and build software together.

#Vivado tools for mac simulator

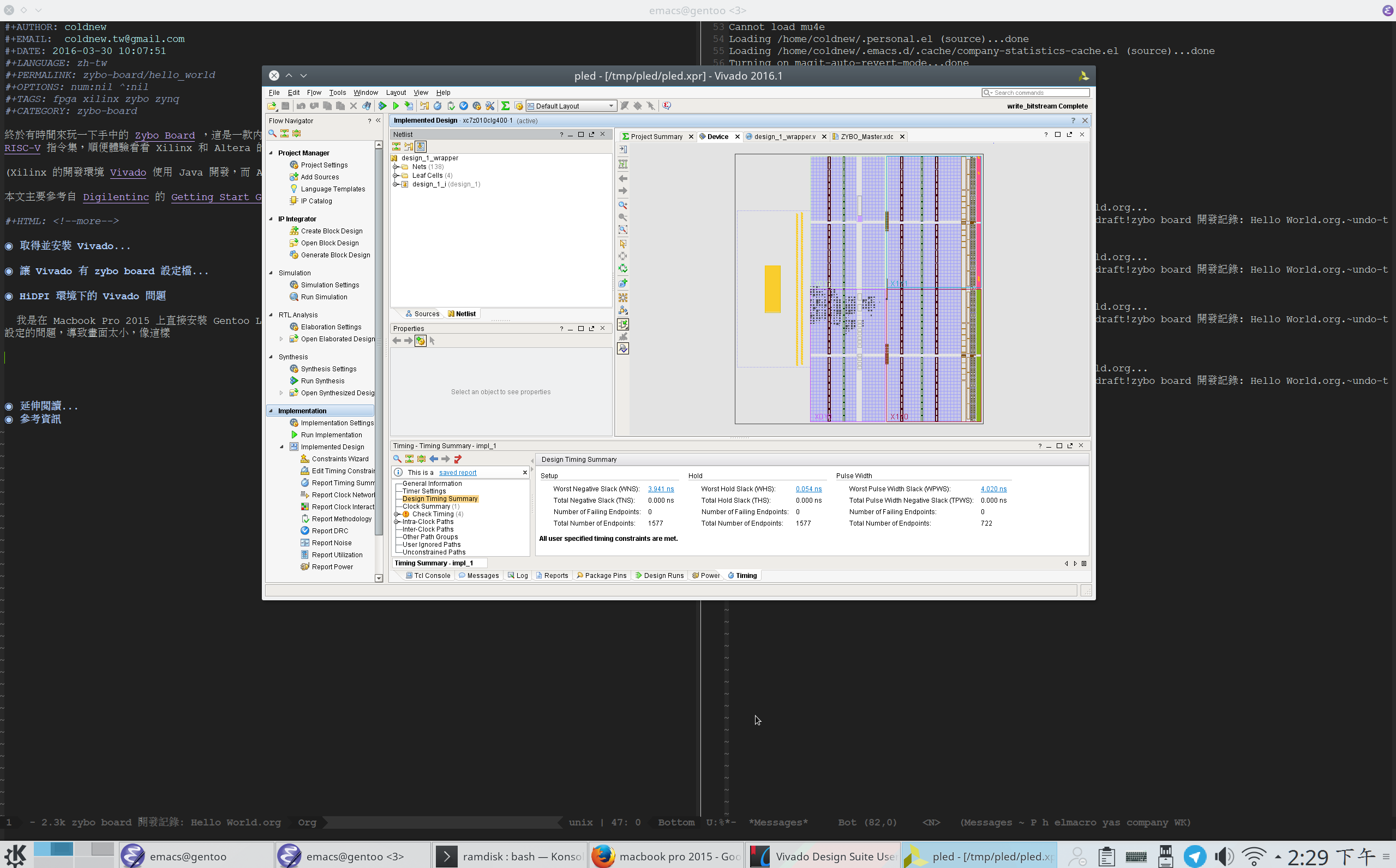

You will use the Vivado simulator to view these waveform signals.

You will use these testbenches to generate various kinds of frames and observe how the core behaves to these received frames. Lab 2 - Advanced Ethernet Frames – Perform a functional simulation of a Vivado Design Suite project, based on the TriMode Ethernet MAC example design, that is provided with several simulation testbenches.You will then modify the testbench to view its effect on core behavior. You will use the Vivado simulator to analyze Ethernet frames and identify the components of the frames. A Vivado Design Suite project, based on the Tri-Mode Ethernet MAC example design, is provided and includes a simulation testbench. This IP is available through the Vivado IP catalog tool. Lab 1 - Exploring Ethernet Frames – Perform a functional simulation of the Tri-Mode Ethernet MAC LogiCORE™ IP.Legal issues, Trademarks and Acknowledgements.Understanding Random Stability in SystemVerilog and UVM.How it Works - Object Detection on an FPGA.

0 kommentar(er)

0 kommentar(er)